10.2 FLİP - FLOP TİPLERİ,

ANALİZİ VE

DÖNÜŞÜMLERİ

10.2.1 Tanım

dir. Q ve

dir. Q ve birbirlerinin tersidir. Yani Q = 1 ise

birbirlerinin tersidir. Yani Q = 1 ise  = 0, Q = 0 ise de

= 0, Q = 0 ise de  =1 olur. Yalnız aşağıdaki doğruluk tablolarında görüleceği gibi Q ve

=1 olur. Yalnız aşağıdaki doğruluk tablolarında görüleceği gibi Q ve  'in aynı olduğu durumlar görülmektedir. Bu durumlar istenmez. Bundan dolayı bu çıkışı veren girişler kullanılmaz. Flip - Flop'lar clock (saat) palsi ile çalışırlar. Bu palsler sayesinde girişlere göre çıkışlar

da değişir. Sayıcıların ve Kaydedicilerin temelini oluştururlar.

'in aynı olduğu durumlar görülmektedir. Bu durumlar istenmez. Bundan dolayı bu çıkışı veren girişler kullanılmaz. Flip - Flop'lar clock (saat) palsi ile çalışırlar. Bu palsler sayesinde girişlere göre çıkışlar

da değişir. Sayıcıların ve Kaydedicilerin temelini oluştururlar.

10.2.2 R - S (Reset - Set) Tipi Flip - Flop

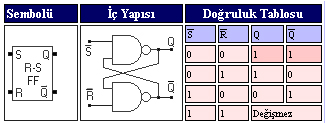

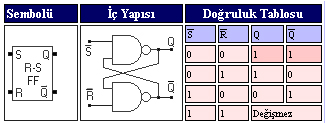

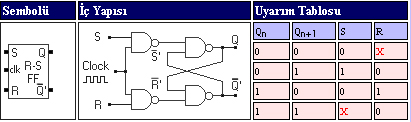

R-S Flip-flop aşağıdaki sembolde görüldüğü gibi S (Set = Kur) ve R (Reset = Sıfırla) isimlerinde iki girişe sahip bir flip-flop'tur. R-S FF devresi ve doğruluk tablosu Şekil 10.2 de gösterilmiştir.

|

|

Şekil 10.2 R-S Flip-Flop sembolü, iç yapısı, doğruluk tablosu |

Yukarıda R-S tipi flip-flop 'un

VEDEĞİL kapıları ile çizilmiş iç yapısı ve doğruluk tablosu görülmektedir. Şekil 10.2'deki ![]() ve

ve  'in 1 olduğu durumda Q ve

'in 1 olduğu durumda Q ve  'in değişmediği görülür. Bu, çıkışların bundan önceki konumunu sakladığını belirtir.

'in değişmediği görülür. Bu, çıkışların bundan önceki konumunu sakladığını belirtir. ![]() ve

ve  'in 0 olduğu durumda ise çıkışların eşit olduğu görülür. Bu durum da flip-floplarda istenmeyen bir durumdur. Bu durumu sağlayan giriş değerleri kullanılmamalıdır.

'in 0 olduğu durumda ise çıkışların eşit olduğu görülür. Bu durum da flip-floplarda istenmeyen bir durumdur. Bu durumu sağlayan giriş değerleri kullanılmamalıdır.

10.2.3 Terslemeli R - S (reset - set) Tipi Flip - Flop

= 1 değerini alır. Bu değer ile 1 nolu ‘VEDEĞİL'

kapısının her iki girişi ‘1’ olacağından, Q = 0 çıkışı oluşur. Sonuç olarak; S = 0,

R = 1 giriş değerlerinde çıkışlarda Q = 0,

= 1 değerini alır. Bu değer ile 1 nolu ‘VEDEĞİL'

kapısının her iki girişi ‘1’ olacağından, Q = 0 çıkışı oluşur. Sonuç olarak; S = 0,

R = 1 giriş değerlerinde çıkışlarda Q = 0,  = 1 değerleri okunur.

= 1 değerleri okunur.

‘VEDEĞİL' kapısı ile oluşturulan FF

devresi girişlerine S=1 ve R=0 değerleri uygulandığında; 1 nolu ‘VEDEĞİL'

kapısının ‘DEĞİL' kapısına bağlı olan girişi ‘0’ olur ve girişlerinden birisi

‘0’ olan bu kapının çıkısı ‘1’ değerlerini alır. Bu durumda, 2 nolu ‘VEDEĞİL'

kapısının her iki girişi ‘1’ olduğundan  = 0 değeri oluşur. Q = 1 ve

= 0 değeri oluşur. Q = 1 ve  = 0

konumunda iken, R = 1 olsa bile NAND–1’in çıkışı ‘1’, NAND-2’nin çıkışı ise '0'

değerlerini saklar.

= 0

konumunda iken, R = 1 olsa bile NAND–1’in çıkışı ‘1’, NAND-2’nin çıkışı ise '0'

değerlerini saklar.

Her iki girişin aynı anda ‘1’ olması

durumunda Q =  = 1 olur ve istenilmeyen bir durum ortaya çıkar. ‘Yasak durum’ olarak

adlandırılan bu durumdaki çalışmadan kaçınmak gerekir.

= 1 olur ve istenilmeyen bir durum ortaya çıkar. ‘Yasak durum’ olarak

adlandırılan bu durumdaki çalışmadan kaçınmak gerekir.

| İç Yapısı | Doğruluk Tablosu | ||||||||||||||||||||

|

|

|

||||||||||||||||||||

Örnek 10.1 R-S Flip-Flop un VEDEĞİL Lojik kapıları ile gerçekleştirilen devresini inceleyelim.

Şekil 10.3 a) sembolü b) VEDEĞİL lojik devresi

10.2.3.1 R - S VEDEĞİL (Latch)

Çalışması

R-S VEDEĞİL ilişkin zamanlama çizelgesi örneği şekil 10.4'te

sunulmaktadır. Buradaki zaman çizelgesi, VE durumlarının değişimine göre 5 zaman

aralığına ayrılmıştır. Her zaman aralığı için latch'in durumu ve alacağı

değerler aşağıdaki şekilde görüldüğü gibidir.

Şekil 10.4 S-R VEDEĞİL zamanlama çizelgesi

1) Bu aralıkta, başlangıç için latch'in

kurulu durumda olduğu (Q = 1) varsayıldı. S ve R girişlerinin etkisiz olduğunu

(mantık 1) kabul ettik. Bunlar, latch'in başlangıç koşulları olarak belirlendi.

2) Bu adımda etkin (0) ve etkisiz (1). Bu nedenle latch "sıfırlanır" ve Q

çıkışı mantık 0 durumuna gelir.

3) Etkisiz duruma (1) döner, fakat latch "sıfırlanmış" olarak (Q = 0) kalır,

ayrıca  de etkisiz (1) durumunu alır. Bu durum bir "değişim - yok" koşuludur.

de etkisiz (1) durumunu alır. Bu durum bir "değişim - yok" koşuludur.

4) Şimdi etkin (0) ve etkisiz (1) olur. Bu nedenle latch bu aralıkta "kurulur" ve Q

çıkışı mantık 1 durumuna geçer.

5) Etkisiz duruma (1) döner ancak latch "kurulu" (Q = 1) durumunda kalır,

bunun nedeni de etkisiz (1) olmasıdır. Bu "değişim - yok" koşuludur.

Şekil 10.5 Burada 5 zaman aralığının her birinde latch durumlarının değişimleri görülebilir.

Örnek 10.2

R-S Flip-Flop VEYADEĞİL Lojik kapıları ile gerçekleştirilen devresini

inceleyelim.

Sıfırla (RESET) durumunda

latchın çıkışı mantık 0 ve Kur (SET) durumunda ise latchın çıkışı

mantık 1 durumunda olur. Bu nedenle devreye SET - RESET (S - R) latchı adı

verilir. S-R latchı etkin-düşük mantık seviyesine göre de tasarlanabilir

(Mantık 0 seviyesi).

Şekil 10.6 a) sembolü b) veyadeğil lojik devresi

Şekil 10.6 'da görüldüğü üzere, latch in

S (SET) ve R (RESET) ile gösterilen iki girişi ve Q ve  ile gösterilen her zaman

birbirinin tamamlayanı olan iki de çıkışı bulunmaktadır. Bir latch in durumu her

zaman Q çıkışının değerleriyle belirlenir. Bunun anlamı, Q = 1 olduğunda

latch in "Kurulu (SET)" durumunu alması; Q = 0 olduğunda ise latch in "Sıfırlanmış (RESET)"

durumunu alması demektir.

ile gösterilen her zaman

birbirinin tamamlayanı olan iki de çıkışı bulunmaktadır. Bir latch in durumu her

zaman Q çıkışının değerleriyle belirlenir. Bunun anlamı, Q = 1 olduğunda

latch in "Kurulu (SET)" durumunu alması; Q = 0 olduğunda ise latch in "Sıfırlanmış (RESET)"

durumunu alması demektir.

Bir S-R latch kurmak için S girişine mantık 1 seviyesi uygulanır. Aynı anda

S ve R girişlerinden sadece biri etkin olmalıdır, bu nedenle S = 1 olduğunda R

girişi mantık 0 seviyesinde etkisiz olmalıdır. Bu nedenle bir S-R latch'i kurulmak

istenirse, R girişine mantık 1 uygulanırken, aynı anda S girişine mantık 0

uygulanmalıdır.

10.2.3.2 S-R VEYADEĞİL Latch'in Çalışması

Şekil 10.7'de bir S - R latch zamanlama diyagramı verilmektedir. Zamanlama diyagramları, sıralı mantık devrelerinin çalışmasını, devrenin girişleri değişirken çıkış durumlarının nasıl değiştiğini grafiksel olarak gösteren çizelgelerdir.

Şekil 10.7 S-R VEYADEĞİL latch zamanlama çizelgesi

Şekil 10.7'de S ve R girişlerinin olası birçok durumu izlenmektedir. S veya R'nin her durum değiştirişinde, latch çıkışlarının durum değiştirip değiştirmedikleri tanımlanmalıdır. Durum değiştirilmesi dikkate alınarak, zaman çizelgesi 8 bölüme ayrılarak analiz edilmektedir.

1) Hem S hem de R etkisizdir. Latchın

çıkışının (Q) başlangıç durumu "R-sıfırla" konumundadır. Bunun için,

latch

"sıfırla" durumunda kalır. Bu "değişim-yok" koşuludur.

2) S etkindir ve latch "kur" durumundadır.

3) S etkisizdir (R etkisiz iken) fakat "kurulu" kalır, çünkü "değişim-yok" koşulu

vardır.

4) R şimdi etkin durumdadır ve latch "kurulu" olur.

5) R etkisizdir (S etkisiz iken), fakat latch "kurulu" durumda kalır, çünkü

"değişim-yok" koşulu vardır.

6) S yeniden etkin kılınır ve latch kurulu duruma geçer.

7) Hem S hem de R şimdi etkindir. Bu durum latcha aynı anda hem "sıfırla" hem

de "kur" olacak şekilde komuta eder. Böyle bir şey ise olanaksız olduğundan,

latchın durumu bilinmez bir durumdur. Buna "tanımsız durum" denir.

8) S şimdi etkisizdir, R hala etkindir, böylece latch "kur" komutunu alır. Her

bir 8 zaman aralığı için latchın durumlarındaki değişimler şekil 10.8'de

sırasıyla incelenerek görülebilir.

Şekil 10.8 Her bir 8 zaman aralığı için

latchın durumlarındaki değişimler görülebilir.

Örnek 10.3 Yükselen kenar tetiklemeli R - S Flip-Flop'un lojik diyagramını ve doğruluk tablosunu inceleyelim.

(a) Lojik Diyagramı

|

|

| (b) Sembolü |

(c) Doğruluk tablosu |

Şekil 10.9 Yükselen kenar tetiklemeli R-S Flip-Flop

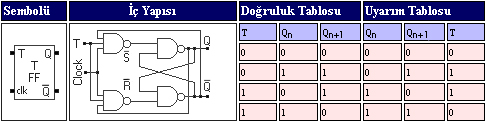

10.2.4 Tetiklemeli R - S (reset - set) Tipi Flip - Flop

Tetiklemeli R-S tipi flip-flop, R-S tipi flip-flop'un önüne iki adet VEDEĞİL kapısı eklenerek elde edilmiştir. Flip-flop'a clock palsi gelmediği sürece çıkışlar değişmez. Yukarıdaki tabloda tetiklemeli R-S flip-flop'un iç yapısı ve uyarım tablosu görülmektedir. Uyarım tablosu flip-floplarla devre tasarımında kullanılır. Tablodaki X 'ler etkisiz elemanlardır. Yani 1 veya 0 olması durumda çıkışlar değişmez. Bazı kaynaklarda (X) yerine (d) de yazılmaktadır. Bu işaretin yerine 0 veya 1 koyulabilir. Ayrıca tablodaki Qn clock

palsinden önceki durumu, Qn+1 ise clock palsinden sonraki durumu temsil etmektedir. Tablo FF

'nin çıkışının Qn'den Qn+1'e geçmesi için S ve R girişlerinin ne olması gerektiğini belirtir.

|

|

Şekil 10.10 Tetiklemeli R-S (reset-set) tipi Flip - Flop |

10.2.4.1

VEDEĞİL Kapılı S - R latchı (S - R latch)

VEDEĞİL Kapılı S-R latchının S ve R

girişlerinin yanı sıra kapı adı verilen ek bir girişi daha vardır. Kapı girişi

(G girişi), latchın ne zaman durumlarını değiştireceğini belirler. Aşağıdaki

şekilde kapılı S-R (VEDEĞİL) latch'inin mantık sembolü ve mantık devresi

sunulmaktadır.

Şekil 10.11 S - R VEDEĞİL latchının mantık sembolü ve mantık devresi

Buradaki S ve R girişleri de daha

önceki kapısız latchlarda olduğu gibi işlev görürler, buna rağmen latch'in

durumunu, G kapı girişine mantık 2 değeri uygulanana kadar değişmeyecektir.

Şekil 10.11'de görüleceği üzere G girişi, S ve R girişlerini G1 ve G2

ile gösterilen iki VEDEĞİL kapısı aracılığıyla geçirerek (1) veya tutar (0).

G = 0 olduğunda, G1 ve G2 VEDEĞİL kapılarının çıkışları S ve R'nin durumlarına

bakılmaksızın 1 olur. G3 ve G4 etkin-düşük mantık seviyeli VEDEĞİL kapıları

oldukları için, G3 ve G4'ün girişlerindeki mantık 1 seviyesi latchı etkisiz

durumda kılar ve bu nedenle durumunda hiçbir değişim olmaz.

G = 1 olduğunda ise, G1 ve G2 çıkışları sırasıyla S ve R durumlarına eşit olur ve

böylece VEDEĞİL latchı, S ve R'ye uygulanan mantık seviyelerinin belirleyeceği

şekilde durum değiştirir.

G girişi, birleşik mantık devrelerinde incelenen "çalışır", "çalışmaz"

durumundaki E ucu gibi işlev görmektedir. Benzer şekilde kapılı S-R VEYADEĞİL

latch'i de tasarlanabilir. Şekil 10.12'de kapılı S-R VEYADEĞİL latchının

mantık devresi gösterilmektedir.

Şekil 10.12 S-R VEYADEĞİL

latchının mantık devresi

10.2.4.2 S - R VEDEĞİL

latchının çalışması

S-R VEDEĞİL latchına ilişkin

zamanlama çizgesi örneği aşağıdaki şekilde verilmektedir. Bu zaman çizgesi S ve

R girişlerinin durum değişimlerine göre farklı 9 zaman aralığına ayrılmıştır.

Latchın her zaman aralığındaki durumları ayrı ayrı Şekil 10.13'de incelenmektedir.

Şekil 10.13 S-R VEDEĞİL latchı zamanlama çizgesi

1) Latch başlangıçta "sıfırlanmıştır" (RESET), fakat bu aralıkta S'nin durumu

mantık 1 seviyesine değişmesine rağmen, G=0 olduğundan latch durumunu

değiştirmeyecektir.

2) Şimdi G'nin durumu mantık 1 seviyesindedir ve latchın S ve R girişleri

"çalışır" durumdadır. Bu aralıkta S mantık 1 durumunda olduğu için,

latch

"kurulu" hale gelir.

3) Bu aralıkta G mantık 0 seviyesinde ve latch girişleri "çalışmaz" durumdadır.

Ancak önceki durum latchlanır, değişim olmaz ve latch "kurulu" kalır. Bu

aralık sürecinde S ve R durum değiştirir, ancak G = 0 olduğundan latchın

durumlarını etkilemezler.

4) Şimdi R etkinken, G mantık 1 seviyesindedir, bu durum ise latchın

"sıfırlanmasına" sebep olur.

5) G mantık 0 seviyesindedir, bu nedenle S ve R'deki değişimler latchın durumunu

etkilemez. Latch "sıfırlanmış" durumunu korur.

6) Şimdi G mantık 1 seviyesindedir, ancak S ve R etkisiz konumdadır. Bu nedenle

latch "sıfırlanmış" durumunu sürdürür.

7) Şimdi G = 1 iken S etkin durumdadır, bunun sonucunda latch "kurulu" (SET)

durumuna geçer.

8) G = 1 iken S ve R etkisiz durumdadır ve latch "kurulu" durumda kalır.

9) Şimdi G=1 iken R etkin duruma geçer, bunun sonucunda latch "sıfırlanır" (RESET)

ve bu durumda kalır.

Bu çalışma aralıklarından da görüldüğü gibi, S ve R girişlerinin durumları

sadece ve sadece G kapı girişi etkin ise latchın durumu üzerinde etkili

olabilirler.

Örnek 10.4 Tetiklemeli R-S Tipi Flip-Flop Devresi

Tetikleme, saat darbesinin “0” dan “1” e yükselen kenarında gerçekleşiyorsa Yükselen Kenar Tetiklemeli Flip-Flop, “1” den “0” a düşen kenarda gerçekleşiyorsa Düşen Kenar Tetiklemeli Flip-Flop adını alır.

|

|

|

(a) Saat darbesi (Clock Pulse) |

(b) “1” düzeyinde tetikleme |

(c) ”0” düzeyinde tetikleme |

Şekil 10.14 Tetikleme sinyali ve düzey tetiklemeleri

|

|

| (a) Yükselen kenar | (b) Düşen kenar |

|

|

(c) Yükselen kenar tetiklemeli |

(d) Düşen kenar tetiklemeli |

Şekil 10.15 Kenar tetiklemesi

10.2.4.3 Pozitif kenar - tetiklemeli S - R

iki durumlunun çalışması

Aşağıdaki şekilde pozitif

kenar-tetiklemeli S-R iki durumluya ilişkin zamanlama çizelgesi

gösterilmektedir. Saat (C) girişi, belirli aralıklarla oluşan sürekli bir darbe

katlarıyla beslenmektedir. Saat darbesinin her pozitif geçişi, iki durumlunun

durumlarını değiştirmesine neden olur.

Şekil 10.16 Pozitif Kenar-Tetiklemeli S-R iki durumlu zamanlama çizelgesi

Saat darbesinin pozitif geçişinin

oluştuğu andaki R ve S girişlerinin durumu, iki durumlunun durumunu belirler.

Şekil 10.16'nın 3 numaralı zaman aralığında iki durumlu, "sıfırlanmış" (RESET) durumunda

kalır, çünkü ikinci saat darbesinin pozitif geçişi oluştuktan sonra S'nin durumu

0'dan 1'e değişmiştir. 4 numaralı zaman aralığı sürecinde, iki durumlu

"kuruludur" (SET), çünkü üçüncü saat darbesi pozitif geçiş yaparken S'nin durumu

1'dir.

10.2.4.4 Negatif kenar - tetiklemeli S - R

iki durumlunun çalışması

İki durumluların tetiklenmesinde,

pozitif ya da negatif kenarla tetiklenmesinin devrenin durumlarını nasıl

etkilediğini görmek için, negatif kenar-tetiklemeli S-R iki durumlunun şekil

10.17'de sunulan zamanlama çizgesinin incelenmesi yararlı olacaktır.

Şekil 10.17 Negatif kenar-tetiklemeli S-R iki durumlu zamanlama çizelgesi

Burada artık saat darbesinin (C) her negatif geçişi, iki durumlunun durumlarını değiştirmesine neden olmaktadır. Saat darbesinin negatif geçişinin oluştuğu andaki R ve S girişlerinin durumu, iki durumlunun durumunu belirler. Şekil 10.17'de 3 numaralı zaman aralığı incelenecek olursa, bu defa iki durumlu "kurulu" (SET) durumdadır, çünkü ikinci saat darbesinin negatif geçişi oluşmadan önce S'nin durumu 0'dan 1'e değişmiştir. 4 numaralı zaman aralığı süresince, iki durumlu hala "kurulu" (SET) kalır, çünkü üçüncü saat darbesi negatif geçiş yaparken S'nin durumu 0'dır. Zaten R'nin durumu da sıfırdır. Buradaki Q çıkışı pozitif kenar-tetiklemeli S-R iki durumlunun Q çıkışı ile karşılaştırılırsa, aynı saat darbesi kullanılmasına ve R-S girişlerinin durumlarının da aynı olmasına rağmen birbirinden oldukça farklı Q çıkışları oluştuğu görülür.

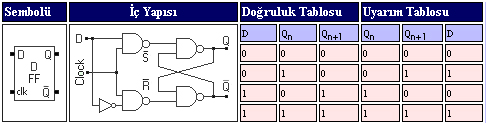

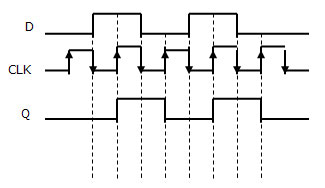

10.2.5 D (Data) Tipi Flip - Flop

Şekil 10.18'deki D

tipi FF 'nin iç yapısında da görüldüğü gibi Tetiklemeli R-S FF 'nin iki ucu arasına değil kapısı eklenerek D

tipi FF elde edilmiştir. Doğruluk tablosunda görüldüğü gibi D tipi FF'ye clock

palsi uygulandığında girişindeki bilgiyi aynen çıkışa iletir. D

tipi FF besleme olduğu sürece bilgi saklayabilir. Clock palsi uygulanmadığı sürece FF

'nin girişleri ne olursa olsun çıkış sabittir. Böylece bilgiyi saklamış olur.

|

| Şekil 10.18 D (data) tipi Flip - Flop |

Aşağıda Şekil 10.19’da yükselen kenar tetiklemeli D tipi Flip-Flop’a ait lojik diyagram, sembol ve doğruluk tablosu gösterilmektedir.

| |

|

(a) Lojik Diyagram

|

|

(b) Sembolü ve R-S denkliği |

(c) Doğruluk Tablosu |

Şekil 10.19 Yükselen kenar tetiklemeli D tipi Flip-Flop

|

| Şekil 10.20 D tipi Flip-Floplarda Tetikleme |

10.2.5.1 D tipi İki durumlunun Pozitif ve Negatif Kenar-Tetiklenmesi

Şekil 10.21'de pozitif

kenar-tetiklemeli D tipi FF'nin iki durumlusuna ilişkin zamanlama çizelgesi sunulmaktadır.

Şekil 10.21 Pozitif kenar-tetiklemeli D tipi FF'nin iki durumlu zamanlama çizelgesi

Benzer şekilde negatif

kenar-tetiklemeli D tipi FF'nin iki durumlu zamanlama çizelgesi oluşturulabilir.

Şekil 10.22'de negatif kenar-tetiklemeli D tipi FF'nin iki durumlu zamanlama çizelgesi

sunulmaktadır.

Şekil 10.22 Negatif kenar-tetiklemeli D tipi FF'nin iki durumlu zamanlama çizelgesi

Yukarıdaki her iki zaman çizelgesinde

de, D ve C girişlerinin mantık durumları aynı olmasına rağmen çıkışların durumu

farklı olmaktadır. İlk şekilde 3. saat darbesi pozitif geçiş yaparken D girişi

mantık 1'dir. Oysa ikinci şekilde 3. saat darbesi negatif geçiş yaparken D

girişi mantık 0'dır. Bu nedenle pozitif ve negatif kenar-tetiklemeli D

iki durumlularının çıkışı farklı olmaktadır.

Örnek 10.5 Pozitif ve Negatif kenar tetiklemeli D flip-flop devresi

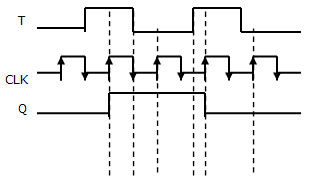

10.2.6 T (Toggle) Tipi Flip - Flop

T tipi FF 'de J-K tipi FF 'nin giriş uçlarının birleşiminden meydana gelmiştir. T

tipi FF 'ye clock pals uygulandığında girişindeki bilginin değilini çıkışa verir.

Aşağıda T tipi FF 'nin iç yapısı, doğruluk tablosu ve uyarım tablosu görülmektedir.

|

|

Şekil 10.23 T (Toggle) tipi Flip - Flop |

Şekil 10.24’de T tipi flip-flop’a ait lojik diyagram, sembol ve doğruluk tablosu gösterilmektedir.

| |

|

| (a) Lojik Diyagram |

|

|

(b) Sembolü |

(c) Doğruluk Tablosu |

Şekil 10.24 Yükselen kenar tetiklemeli T Flip-Flop

|

| Şekil 10.25 Yükselen kenar tetiklemeli T tipi Flip Flop |

10.2.6.1 T tipi İki durumlunun Pozitif ve Negatif Kenar-Tetiklenmesi

Şekil 10.26'da pozitif kenar-tetiklemeli T tipi FF'nin

iki durumlusuna ilişkin zamanlama çizelgesi sunulmaktadır.

Şekil 10.26 Pozitif kenar-tetiklemeli T tipi FF'nin iki durumlusu zamanlama çizelgesi

Benzer tarzda negatif kenar-tetiklemeli T tipi FF'nin iki durumlusunun zamanlama çizelgesi oluşturulabilir. Şekil 10.27'de negatif kenar-tetiklemeli T tipi FF'nin iki durumlusuna ilişkin zamanlama çizelgesi sunulmaktadır.

Şekil 10.27

Negatif kenar-tetiklemeli T tipi FF'nin iki durumlusu zamanlama çizelgesi

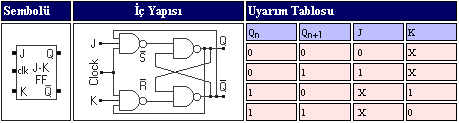

10.2.7 J - K Tipi Flip - Flop

Şekil 10.28 'deki tabloda JK FF

'nin sembolü, iç yapısı ve uyarım tablosu görülmektedir.

|

| Şekil 10.28 J - K tipi Flip - Flop |

Şekil 10.29 ’de yükselen kenar tetiklemeli J-K tipi Flip-Flop’a ait lojik diyagram, sembol ve doğruluk tablosu gösterilmektedir.

| |

|

| (a)Lojik Diyagram |

|

|

|

(b) Sembolü |

(c) Doğruluk Tablosu |

Şekil 10.29 Yükselen kenar tetiklemeli J-K tipi Flip-Flop

10.2.7.1 J-K Tipi FF'nin İki durumlusunun Çalışması

Şekil 10.30'da

pozitif kenar-tetiklemeli J-K tipi FF'nin iki durumlusuna ilişkin örnek zamanlama çizelgesi

sunulmaktadır.

Şekil 10.30 Pozitif kenar-tetiklemeli J-K tipi FF'nin iki durumlu zamanlama çizelgesi

Saat darbesinin ilk "geçişi" sırasında J=1 ve K=1 ve iki durumlunun şimdiki çıkışı mantık 1'dir. Bunun için gelecek durum, 2 numaralı zaman aralığı süresinde "sıfırlanmış" (RESET), yani mantık 0 durumundadır. Saat (C) darbesinin 3. geçişinde J=0 ve K=0 durumundadır. İki durumlunun sıfırlanacağını (RESET) belirtir, ancak iki durumlu zaten "sıfırlanmış" (RESET) durumda olduğundan 3 numaralı zaman aralığı süresinde hiçbir değişim olmaz. Saat'in 4. geçişinde J=0 ve K=0 durumundadır ve bu durum değişim-yok koşulunu belirtmektedir. Bu nedenle iki durumlu, 4 numaralı zaman aralığı sürecinde "sıfırlanmış" (RESET) durumunda kalır. Saatin 5. geçişinde J=1 ve K=0 durumundadır ve iki durumlu 5 numaralı zaman aralığı süresinde "kurulu" (SET) durumunda olur. Saatin 6. geçişinde J=1 ve K=1 durumundadır, bundan dolayı iki durumlunun gelecek durumu şimdiki durumunun tümleyeni durumunda olur ve 6 numaralı zaman aralığı sürecinde iki durumlu "sıfırlanmış" (RESET) durumundadır.

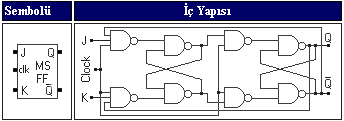

10.2.8 Master - Slave Tipi Flip - Flop

Şekil 10.31'de Master - Slave FF 'nin sembolü ve iç yapısı görülmektedir.

|

| Şekil 10.31 Master - Slave tipi Flip - Flop |

|

| Şekil 10.32 Master - Slave tipi Flip - Flop |

Tetikleme girişi (CP) düşen kenar (↓) olduğu zaman DEĞİL kapısı çıkışı uydu Flip-Flop tetikleme girişini (CP) yükselen kenar (↑) yapacağından uydu Flip-Flop yetkilenir ve R-S girişlerinde ana Flip-Flop’un çıkışları olan Y ve ![]() görülür. Bu durumda uydu

Flip-Flop’un Q çıkışında Y,

görülür. Bu durumda uydu

Flip-Flop’un Q çıkışında Y,  çıkışında

çıkışında ![]() görülür. Ana Flip-Flop tetikleme girişinde bir düşen kenar olduğundan girişteki değişim ne olursa olsun bir önceki durum korunacaktır. Tetikleme girişinin bir yükselen kenar (↑) olması halinde uydu tetikleme girişi bir düşen kenar (↓) olacağından girişlerdeki değişim ne olursa olsun çıkışa yansımayacaktır. Ana Flip-Flop tetikleneceğinde çıkışlarda girişlere uygulanan değerlere eşit olacaktır. Saat darbesinin pozitif geçişinde ya da

negatif geçişinde durum değiştiren iki durumlular kenar-tetiklemeli

iki durumlular olarak adlandırılmaktadır. Burada iki durumluyu tetiklemek için

gereken şey tam bir saat darbesinin kenarlarıdır. Fakat tam bir saat darbesi gerektiren iki durumluları kullanan

uygulamaların sayısı da oldukça fazladır. Tam bir saat darbesinde bir pozitif

geçiş ve bir negatif geçiş yapılır. Tam bir saat darbesi alarak durumları

değişen iki durumluya ana-uydu veya darbe tetiklemeli iki durumlu

denir.

görülür. Ana Flip-Flop tetikleme girişinde bir düşen kenar olduğundan girişteki değişim ne olursa olsun bir önceki durum korunacaktır. Tetikleme girişinin bir yükselen kenar (↑) olması halinde uydu tetikleme girişi bir düşen kenar (↓) olacağından girişlerdeki değişim ne olursa olsun çıkışa yansımayacaktır. Ana Flip-Flop tetikleneceğinde çıkışlarda girişlere uygulanan değerlere eşit olacaktır. Saat darbesinin pozitif geçişinde ya da

negatif geçişinde durum değiştiren iki durumlular kenar-tetiklemeli

iki durumlular olarak adlandırılmaktadır. Burada iki durumluyu tetiklemek için

gereken şey tam bir saat darbesinin kenarlarıdır. Fakat tam bir saat darbesi gerektiren iki durumluları kullanan

uygulamaların sayısı da oldukça fazladır. Tam bir saat darbesinde bir pozitif

geçiş ve bir negatif geçiş yapılır. Tam bir saat darbesi alarak durumları

değişen iki durumluya ana-uydu veya darbe tetiklemeli iki durumlu

denir.

Şekil 10.33 Master - Slave tipi Flip - Flop

10.2.9 Flip-Flop'ların Analizi

Sıralı devrelerde J-K, R-S veya T Tipi Flip-flop'lar kullanıldığında sonraki durum ve çıkışın analizi yapılabilir. Bunun için şu iki adım takip edilir.

1.ADIM: Her bir Flip-flop giriş fonksiyonuna ait ifade, şimdiki durum ve giriş değişkenleri açısından belirlenir.Sıralı devrenin Flip-floplara girişler üreten kısmı, Flip-flop giriş fonksiyonları veya giriş eşitlikleri adı verilen bir grup Boolean cebri tipindeki fonksiyonlar ile tanımlanmaktadır. Bir Flip-flop'un giriş fonksiyonunu belirlemek için iki adet harf kullanılır. Bunlarda ilki giriş adını, diğeri ise Flip-flop'un adını alır. Örneğin; JA = Bx + B y ve KA = AÅx fonksiyonlarını ele alalım: Burada JA ve KA iki Boolean değişkenini göstermektedir . Değişkenlerin ilk harfleri, kullanılacak olan J-K Flip-flop'un J ve K girişlerini, ikinci harf (A) ise Flip-flop adını (A Flip-flop'u) belirtir. Bu Flip-flop'un çıkışı A tümleyeni de A olur.

2.ADIM: Sonraki durumu belirlemek için ise Flip-flop karakteristik tablosundan yararlanılır. Aşağıda dört tip Flip-flop'a ait karakteristik tabloları görülmektedir. Burada sonraki durum (Qp+1), girişlerin ve şimdiki durumun (Qp) bir fonksiyonu olarak tanımlanmaktadır. Aşağıdaki tablolarda Qp ve Qp+1 daha önceki tablolarda ifade edilen Qn ve Qn+1 terimleri ile aynı anlama sahiplerdir.

|

S |

R |

Qp+1 |

Durum |

|---|---|---|---|

|

0 |

0 |

Qp |

Değişmez |

|

0 |

1 |

0 |

Reset |

|

1 |

0 |

1 |

Set |

|

1 |

1 |

-- |

Tanımsız |

a) R-S Flip-Flop karakteristik tablosu

|

J |

K |

Qp+1 |

Durum |

|---|---|---|---|

|

0 |

0 |

Qp |

Değişmez |

|

0 |

1 |

0 |

Reset |

|

1 |

0 |

1 |

Set |

|

1 |

1 |

Qp |

Tümleyen |

b) J-K Flip-Flop karakteristik tablosu

|

D |

Qp+1 |

Durum |

|---|---|---|

|

0 |

0 |

Reset |

|

1 |

1 |

Set |

c) D Tipi Flip-Flop karakteristik tablosu

|

T |

Qp+1 |

Durum |

|---|---|---|

|

0 |

Değişmez |

|

|

1 |

Tümleyen |

d) T Tipi Flip-Flop karakteristik tablosu

Şekil 10.34 Dört tip Flip-flop'a ait karakteristik tablolar

Şekil 10.34'te görüldüğü gibi, D Tipi Flip-flop'lu sıralı devrenin analizi Flip-flop girişleriyle sonraki durum (Qp+1) arasındaki ilişki şimdiki durumdan (Qp) bağımsız olup doğrudan sonraki durum denklemlerinden elde edilir. Yani Qp+1 = D olduğundan sonraki durum değeri, D girişinin ikili mantık değerinden doğrudan elde edilir. J-K Flip-flop'un karakteristik tablosuna göre analiz yapıldığında durum şu şekilde değişir:

1) J = K = 0 durumunda; sonraki durum şimdiki duruma eşit

olur. Yani, Qp+1 = Qp olur.

2) J = 0, K = 1 durumunda; saat darbesi Flip-flop'u başlangıç durumuna

getirir. Yani , Qp+1 = Qp+1 = 0 olur.

3) J = 1, K = 0 durumunda; Flip-flop Set konumunda olup Qp+1 =1 olur.

4) J = K = 1 durumunda ise; sonraki durum şimdiki durumun tümleyenine

eşittir. Yani, Qp+1 = Qp

olur.

J-K Flip-flop en kapsamlı özelliğe sahip olup diğer Flip-flopların özelliklerini de kapsamaktadır. Örneğin R-S tipi Flip-flop, tanımsız durum ( her iki girişin 1 olması durumu) dışında S yerine J , R yerine de K kullanılarak elde edildiğinde J-K Flip-flop gibi davranır. Benzer şekilde, J ve K girişlerinin birbirine bağlanmasıyla tek girişli T Tipi Flip-flop özelliğini gösterir. Yani her iki girişin '0' olması (Qp+1 = Qp) ve her iki girişin '1' olması (Qp+1 = Qp) durumlarında J-K ve T Flip-flop'un sonraki durumları aynıdır.

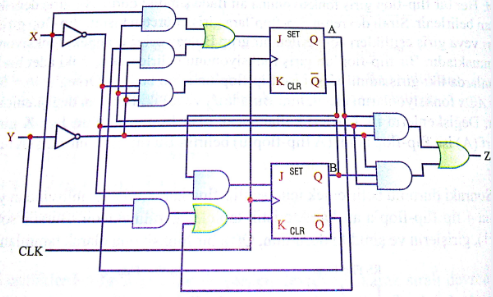

Örnek 10.6 A ve B biçiminde iki J-K Flip-flop ve bunlara X ve Y girişi ve Z çıkışı ekleyerek oluşan sıralı devrenin Flip-flop girişleri ve çıkışa ait eşitlikleri aşağıdaki gibi olsun;

JA = Bx + B y KA = Bx y JB = A x KB = A + xy Z = Ax y + Bx y

Devre yukarıdaki Flip-flop giriş fonksiyonları ve çıkış fonksiyonuna göre aşağıda Şekil 10.35'de görüldüğü gibi çizilir.

Şekil 10.35 Fonksiyonlara göre çizilen mantık devresi

Çizim yapılırken öncelikle Flip-flop'lardan başlamak kolaylık sağlar. Daha sonra giriş ve çıkış değişkenlerinin bağlantısı yapılır. J-K Flip-flop için karakteristik denklemler;

A(p + 1) = JAA + KAA

B(P + 1) = JBB + KBB

Karakteristik denklenmler ve yukarıda verilen eşitliklerle çizilen devrenin durum tablosu elde edilir.

|

Şimdiki Durum |

Girişler |

Sonraki Durum |

Flip-Flop Girişleri JA KA JB KB |

Çıkış |

| 0 0 | 0 0 | 1 1 | 1 0 1 0 | 1 |

| 0 0 | 0 1 | 0 1 |

0 0 1 0 |

0 |

| 0 0 | 1 0 | 1 0 | 1 0 0 0 | 0 |

| 0 0 | 1 1 | 0 0 | 0 0 0 1 | 0 |

| 0 1 | 0 0 | 0 1 | 0 1 1 0 | 0 |

| 0 1 | 0 1 | 0 1 | 0 0 1 0 | 0 |

| 0 1 | 1 0 | 1 1 | 1 0 0 0 | 0 |

| 0 1 | 1 1 | 1 0 | 1 0 0 1 | 0 |

| 1 0 | 0 0 | 0 0 | 1 1 0 1 | 1 |

| 1 0 | 0 1 | 0 0 | 0 0 0 1 | 0 |

| 1 0 | 1 0 | 1 0 | 1 0 0 1 | 0 |

| 1 0 | 1 1 | 1 0 | 0 0 0 1 | 0 |

| 1 1 | 0 0 | 0 0 | 0 1 0 1 | 1 |

| 1 1 | 0 1 | 1 0 | 0 0 0 1 | 0 |

| 1 1 | 1 0 | 1 0 | 1 0 0 1 | 0 |

| 1 1 | 1 1 | 1 0 | 1 0 0 1 | 0 |

Şekil 10.36 Örnek sıralı devrenin durum tablosu

10.2.10 Flip - Flop Dönüşümleri

İki adet Flip-flop verilsin ve bu Flip-flopların birini ve mantık kapılarını kullanarak diğer Flip-flop'u tasarlamaya çalışalım. Bunun için takip edilecek yol şöyledir. Flip-floplarımız AB ve CD olsun. Diyelim ki CD Flip-flop'unu ve mantık kapılarını kullanarak AB Flip-flop'unu tasarlayalım. Bunun için ilk olarak çıktıların olası birleşimlerini bulup,bu birleşimler için Flip-flopların girdilerini içeren birleşik uyarım tablosu aşağıdaki gibi oluşturulur.

|

Qp |

Qp+1 | A | B | C |

D |

|---|---|---|---|---|---|

| 0 | 0 | ||||

| 0 | 1 | ||||

| 1 | 0 | ||||

| 1 | 1 |

Şekil 10.37 AB ve CD Flip-floplarının birleşik uyarım tablosu

Yukarıdaki tabloyu kullanarak C ve D fonksiyonlarını Qp, A ve B türünden ifade ederiz. Bunun için gerekirse karnough haritası da çıkarabiliriz. Son olarak da CD Flip-flop'unun girişlerine C ve D fonksiyonlarının gerçekleştirimleri bağlanır. Şimdi bununla ilgili bir örnek çözelim;

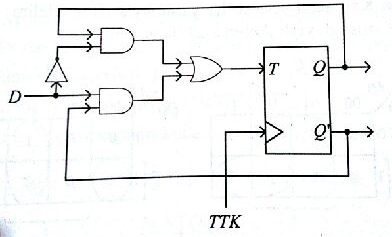

Örnek 10.6 T Tipi Flip-flop'u ve mantık kapılarını kullanarak D Tipi Flip-flop'u tasarlayınız.

İlk olarak D ve T Tipi Flip-flopların uyarım tablolarını aşağıdaki gibi oluşturalım.

|

Qp |

Qp+1 | D | T |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Şekil 10.38 D ve T tipi Flip-flopların birleşik uyarım tablosu

Daha sonra yukarıdaki tablo kullanılarak T fonksiyonunu Qp ve D türünden T = Qp Å D şeklinde ifade edilir.

Şekil 10.39 D Tipi Flip-flop'un, T Tipi Flip-flop ve mantık kapıları kullanılarak tasarlanması

Örnek 10.7 AB ve CD Flip-flop'larının karakteristik tabloları aşağıda verilmiştir. AB Flip-flop'unu CD Flip-flop'u ve mantık kapıları kullanarak tasarlayınız.

|

A |

B | Qp+1 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | Qp |

| 1 | 1 | Qp |

|

C |

D | Qp+1 |

|---|---|---|

| 0 | 0 | Qp |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Qp |

Şekil 10.40 AB ve CD Flip-flop'larının karakteristik tabloları

Yukarıdaki karakteristik tablolarını kullanarak AB ve CD Flip-flop'larının uyarım tablolarını elde edelim ve bu iki tabloyu tek bir tablo halinde aşağıdaki gibi gösterelim.

|

Qp |

Qp+1 | A | B | C |

D |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 |

Şekil 10.41 AB ve CD Flip-flop'larının birleşik uyarım tablosu

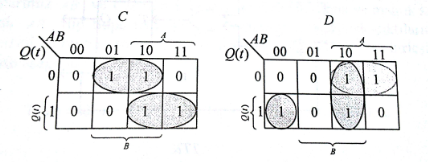

Yukarıdaki uyarım tablosunu kullanarak C ve D fonksiyonlarını Qp, A ve B türünden Karnough haritası yardımıyla ifade edelim. C ve D fonksiyonları için karnough haritası aşağıda şekilde gmsterildiği gibi oluşturulur.

Şekil 10.42 C ve D fonksiyonları için karnough haritası

Yukarıdaki karnough haritası kullanılarak C ve D fonksiyonları C = QpA + QpB D = QpA + (AB +A B)( AB + Qp) şeklinde bulunur.

Yukarıdaki eşitlikleri kullanarak AB Flip-flop'unu CD Flip-flop'u ve mantık kapıları kullanarak aşağıdaki şekilde gösterildiği gibi tasarlayabiliriz.

Şekil 10.43 AB Flip-flop'unun CD Flip-Flop'u kullanılarak tasarlanması

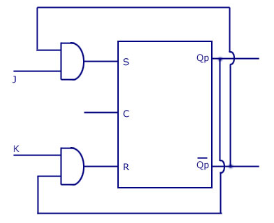

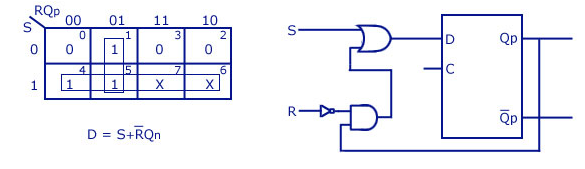

10.2.10.1 S-R Flip-Flop'un J - K Flip-Flop'a Dönüşümü

Aşağıdaki çizimde gösterildiği gibi S-R flip-flop, J-K flip-flop'a harici olarak bağlanır. J-K flip-flop'un girişleri, S-R flip-flop kombinasyonel devresinin çıkış uçları olur.

Dönüşüm için uyarım tablosunda görüldüğü gibi şimdiki durumu Qp ve sonraki durumu ise J ve K girişleri Qp+1 belirler. J-K kombinasyonlarının her biri için Qp ve Qp+1 değerleri bulunur.Daha sonra karşılık gelen S-R değerleri yazılarak bu kombinasyonun Qp'den Qp+1'e geçmesi için S ve R girişlerinin ne olması gerektiği belirlenir.

|

J |

K | Qp | Qp+1 | S |

R |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | X |

| 0 | 0 | 1 | 1 | X | 0 |

| 0 | 1 | 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | X | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 |

a) Uyarım Tablosu

b) Karnough Haritası

c) Lojik Diyagram

Şekil 10.44 S-R Flip-flop'un J-K Flip-Flop'a

dönüşümünün uyarım tablosu,

karnough haritası ve lojik diyagramı

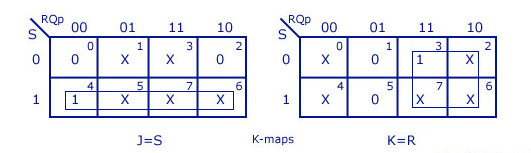

10.2.10.2 J - K Flip-Flop'un S - R Flip-Flop'a Dönüşümü

Anlaşılacağı üzere yukarıdaki dönüşümün tam tersi bir durumdur.Bu sefer J-K flip-flop harici olarak bağlanmaktadır ve J-K FF kombinasyonel devrenin çıkışı olacaktır. Bu sebeple J-K FF değerleri, S-R FF ve Qp cinsinden elde edilmesi gerekir. S=1 ve R=1 olduğu durumlarda çıkışa izin verilmez ve geçersiz kabul edilir.

|

S |

R | Qp | Qp+1 | J |

K |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | X |

| 0 | 0 | 1 | 1 | X | 0 |

| 0 | 1 | 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 | X | 1 |

| 1 | 0 | 0 | 1 | 1 | X |

| 1 | 0 | 1 | 1 | X | 0 |

| 1 | 1 | Yasak | Geçersiz | ||

| 1 | 1 | Yasak | Geçersiz | ||

a) Uyarım Tablosu

b) Karnough Haritası

c) Lojik Diyagram

Şekil 10.45 J-K Flip-flop'un S-R Flip-flop'a dönüşümünün uyarım

tablosu,

karnough haritası ve lojik diyagramı

10.2.10.3 S - R Flip-Flop'un D Tipi Flip-Flop'a Dönüşümü

Şekilde görüldüğü gibi D Tipi flip-flop ve Qp açısından S-R flip-flop'un uyarım tablosu yardımıyla karnough haritasının oluşumu ve lojik diyagramı.

| D | Qp | Qp+1 | S |

R |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | X |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | X | 0 |

a) Uyarım Tablosu

b) Karnough Haritası ve Lojik Diyagram

Şekil 10.46 S-R Flip-flop'un D Tipi Flip-Flop'a dönüşümünün uyarım

tablosu,

karnough haritası ve lojik diyagramı

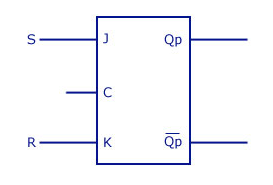

10.2.10.4 D Tipi Flip-Flop'un S - R Flip-Flop'a Dönüşümü

Şekilde görüldüğü gibi S - R flip-flop ve Qp açısından D Tipi flip-flop'un uyarım tablosu yardımıyla karnough haritasının oluşumu ve lojik diyagramı.

|

S |

R | Qp | Qp+1 | D |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | Yasak | Geçersiz | |

| 1 | 1 | Yasak | Geçersiz | |

a) Uyarım Tablosu

b) Karnough Haritası ve Lojik Diyagram

Şekil 10.47 D Tipi Flip-flop'un S-R Flip-flop'a dönüşümünün

uyarım tablosu,

karnough haritası ve lojik diyagramı

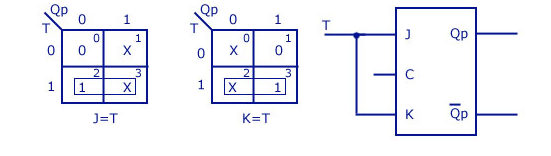

10.2.10.5 J-K Flip-Flop'un T Tipi Flip-Flop'a Dönüşümü

T Tipi flip-flop ve Qp açısından J - K flip-flop'un uyarım tablosu yardımıyla karnough haritasının oluşumu ve lojik diyagramı aşağıdaki şekillerde görüldüğü gibidir.

| T | Qp | Qp+1 | J | K |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | X |

| 0 | 1 | 1 | X | 0 |

| 1 | 0 | 1 | 1 | X |

| 1 | 1 | 0 | X | 1 |

a) Uyarım Tablosu

b) Karnough Haritası ve Lojik Diyagram

Şekil 10.48 J-K Flip-flop'un T Tipi Flip-flop'a dönüşümünün tablosu, karnough haritası ve lojik diyagramı

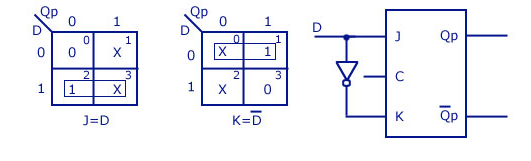

10.2.10.6 J-K Flip-Flop'un D Tipi Flip-Flop'a Dönüşümü

D Tipi flip-flop ve Qp açısından J-K flip-flop'un uyarım tablosu yardımıyla karnough haritasının oluşumu ve lojik diyagramı aşağıdaki şekillerde görüldüğü gibidir.

| D | Qp | Qp+1 | J | K |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | X |

| 0 | 1 | 0 | X | 1 |

| 1 | 0 | 1 | 1 | X |

| 1 | 1 | 1 | X | 0 |

a) Uyarım Tablosu

b) Karnough Haritası ve Lojik Diyagram

Şekil 10.49 J-K Flip-flop'un D Tipi Flip-flop'a dönüşümünün uyarım tablosu , karnough haritası ve lojik diyagramı

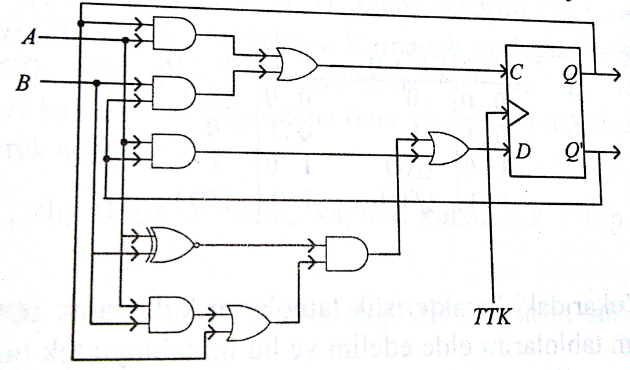

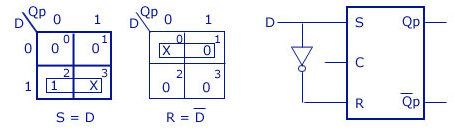

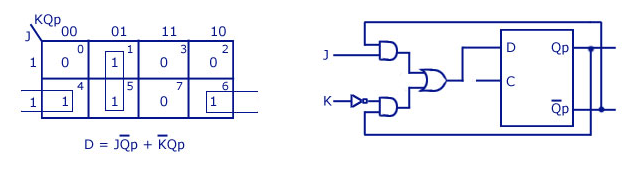

10.2.10.7 D Tipi Flip-Flop'un J-K Flip-Flop'a Dönüşümü

J-K flip-flop ve Qp açısından D Tipi flip-flop'un uyarım tablosu yardımıyla karnough haritasının oluşumu ve lojik diyagramı aşağıdaki şekillerde görüldüğü gibidir.

|

J |

K | Qp | Qp+1 | D |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

a) Uyarım Tablosu

b) Karnough Haritası ve Lojik Diyagram

Şekil 10.50 D Tipi Flip-flop'un J-K Flip-flop'a dönüşümünün uyarım tablosu, karnough haritası ve lojik diyagramı

10.2.10.8 D Tipi Flip-Flop'un T Flip-Flop'a Dönüşümü

Burada D flip-flop’un T flip-flop’a dönüşümünü inceleyeceğiz. Bu amaçla ilk

olarak dönüşümü amaçlanan T flip-flop’un uyarım tablosu aşağıdaki gibi

oluşturulur.

|

T |

Qt |

Qt+1 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Şekil 10.51 D Tipi Flip-flop'un T Flip-flop'a dönüşümünün uyarım tablosu

Bilindiği gibi D flip-flop’un tek bir input’u vardır. D flip-flop’un inputları

ile T flip-flop’un inputları birlikte değerlendirildiğinde oluşacak uyarım

tablosu aşağıda şekilde oluşturulur.

|

T |

Qt+1 |

Qt |

D |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

Şekil 10.52 D Tipi Flip-flop'un ile T Flip-flop'un ortak uyarım tablosu

Yukarıdaki tabloyu kullanarak aşağıdaki lojik fonksiyon elde edilir:

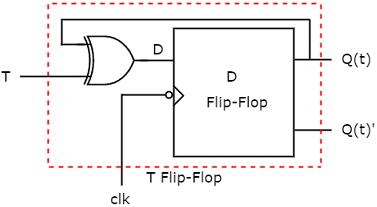

Yukarıdaki lojik fonksiyonuna ait devreyi oluşturmak için bir XOR kapısıyla D

flip-flop’una ihtiyaç vardır. XOR kapısı T inputunun XOR’lanmış değerini

oluşturur ve bunu D flip-flopu’na input olarak verir. Dolayısıyla devre genel

olarak tek bir input (T) ile iki tane outputtan (Q(t) & Q(t)’) oluşacak şekilde

aşağıdaki resimde görüldüğü gibi oluşturulur.

Şekil 10.53 D Tipi Flip-flop'un ile

T Flip-flop'a çevrildiği devre şeması