8.5 MULTIPLEXER (Çoklayıcılar)

8.5.1 Tanım

Multiplexer devresi, bir çok giriş hattındaki bilgilerden birisini seçerek sadece uygun olan birini çıkışa aktaran devredir. Bir giriş hattının seçilmesi, seçme bitleri ile kontrol edilmektedir. Multiplexer kısaca MUX olarak bilinir. Multiplex'in

Türkçe karşılığı ise 'veri çoklayıcılar' anlamına gelmektedir. 2n giriş hatlı bir MUX devresinde n tane select bit

(seçme biti) vardır. MUX’ a veri seçici veya bilgi seçici adı verilmektedir.

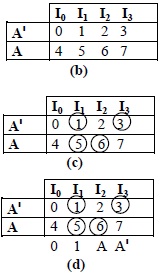

Mux devre yapımında NMOSFET’ler kullanılır. Aşağıdaki şekil a’da NMOS sembolü

verilmiştir. Vin giriş, Vout çıkışı Vg kapı girişi ile kontrol edilir. Tek yönlü bir kapıdır. Vg girişine mantık 0 (GND) ve

mantık 1 (Vcc) sinyalleri uygulanır. Vg girişine mantık 0 uygulandığında N1 pasiftir. Vg girişine mantık 1 uygulandığında N2 aktiftir ve Vin ikilik bilgisi Vout çıkışına aktarılır.

|

|

Şekil 8.50 a) NMOS b) iki NMOS ile yapılan mantık sembolü c) 2:1MUX mantık sembolü |

Şekil b’de iki NMOS kapı kullanılarak bir MUX devresi evde edilir. A ve B

bilgi girişleridir. S seçici girişidir. S seçici girişine mantık 1

uygulandığında N1 aktif olur ve A ikilik bilgisi Z çıkışına aktarılır. N2

pasiftir. S seçici girişi mantık 0 olduğunda N2 kapısı aktif olur ve B ikilik

bilgisi Z çıkışına aktarılır.

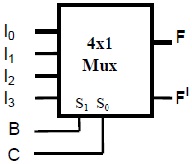

8.5.2 4’ten 1’e Multiplexer

4x1 MUX devresinde 4 giriş hattı olduğu için (2n = 4 olduğundan n = 2) 2 tane kontrol biti olması gerekir.

Bu devreye uygun doğruluk tablosu;

|

Tablo 8.27 4x1 MUX devresine uygun doğruluk tablosu |

Select Bits |

OUTPUT |

|

S2 |

S1 |

F |

0 |

0 |

D0 |

0 |

1 |

D1 |

1 |

0 |

D2 |

1 |

1 |

D3 |

Bu doğruluk tablosunda, S2 = S1 = 0 ise MUX devresinin çıkışında sadece D0 girişi olacaktır. S2 = 0, S1 = 1 ise çıkışta D1 girişi görülecektir. S2 = 1, S1 = 0 ise çıkışta D2 girişi, S2 = S1 = 1 ise çıkışta D3 girişi olacaktır. Buradan anlaşılacağı gibi Select bitlerinin konumuna göre girişlerden sadece birisi çıkışa aktarılacaktır. Birçok giriş bilgisinden sadece bir tanesi çıkışa aktarılır. Doğruluk tablosundaki F çıkışı şu şekilde yazılabilir.

F =![]() .

.![]() .DO +

.DO + ![]() .S1.D1 + S2.

.S1.D1 + S2.![]() .D2 + S2.S1.D3

.D2 + S2.S1.D3

|

|

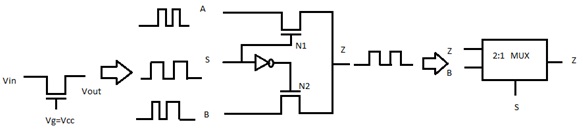

Şekil 8.51 4x1 Mux Uygulaması |

|

Şekil 8.52 4x1 Mux Gösterimi |

Örnek 8.16 4’ten 1’e çoklayıcı lojik devresini tasarlayınız.

4'ten 1’e çoklayıcı devresinin lojik kapılar ile tasarımı yapılırken seçme uçları dikkate alınır. Her VE kapısına bir adet fazladan data hattı bağlanır. Bu nedenle her data (bilgi) hattı için bir kapının gerekli olduğu dikkat edilmelidir. Bu şartları sağlayan doğruluk tablosu ve devrenin Lojik Kapılarla gerçekleştirilmiş hali aşağıda verilmiştir.

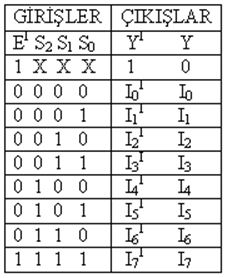

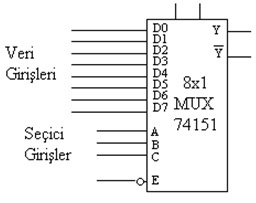

8.5.3 8’den 1’e Multiplexer

8x1 MUX devresinde 8 giriş hattı ve 1 çıkış vardır. 2n = 8 formülüne göre n = 3 olduğu için 8x1 MUX devresinde 3 tane kontrol biti vardır. Buna göre S2 = S1 = S0 = 0 olduğu zaman çıkışta I0 girişi görülür. S2 = 1, S1 = S0 = 0 olduğu zamanda çıkışta I4 girişi alınmış olur.

|

Tablo 8.28 8x1 MUX devresine uygun doğruluk tablosu |

Select Bits |

OUTPUT |

||

S2 |

S1 |

S0 |

Z |

0 |

0 |

0 |

I0 |

0 |

0 |

1 |

I1 |

0 |

1 |

0 |

I2 |

0 |

1 |

1 |

I3 |

1 |

0 |

0 |

I4 |

1 |

0 |

1 |

I5 |

1 |

1 |

0 |

I6 |

1 |

1 |

1 |

I7 |

![]()

Örnek 8.17 8'den 1'e multiplexer devresini tasarlayınız.

|

|

Şekil 8.53 8x1 MUX devresinin lojik sembolü |

Yapılan örneklerde S2 = S1 = 0 ve S0 = 1 uygulandığında I1 girişindeki +5V’luk bilgi Z çıkışında S2 = S0 = 1 ve S1 = 0 konumunda da I5 girişindeki +5V’luk bilgi Z çıkışından alınmıştır. Bu örnek uygulamalarda da kontrol girişlerinden aldığı konuma bağlı olarak girişlerden sadece biri çıkışa aktarılmıştır.

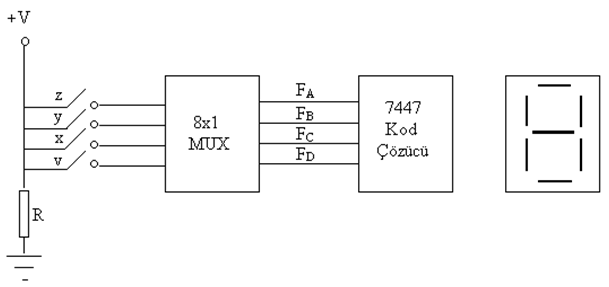

Örnek 8.18 8 giriş 4 çıkışlı MUX devresi uygulama olarak veri seçici devresi

|

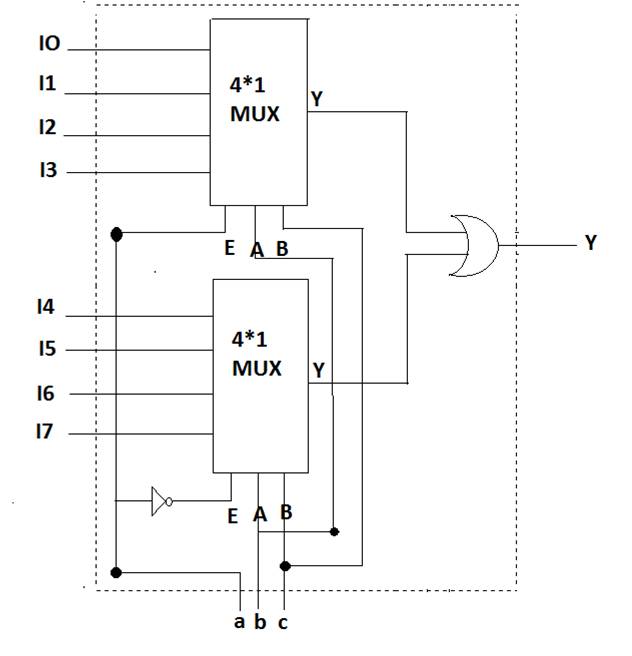

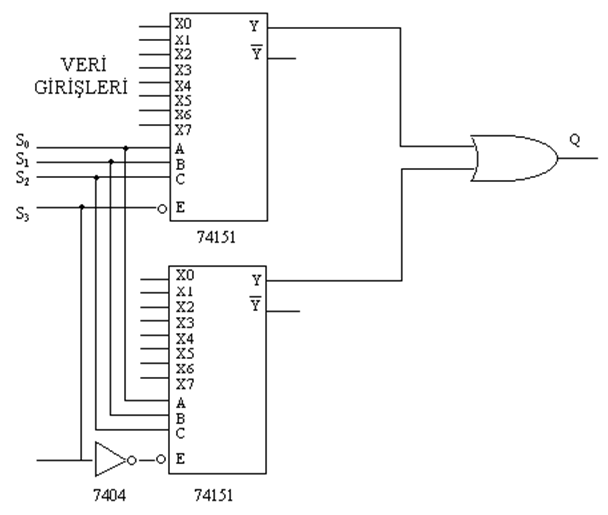

Örnek 8.19 4x1 MUX ile 8x1 MUX elde eden devreyi tasarlayınız.

4’ten 1’e Multiplexer'ların giriş uçları

8’den 1’e Multiplexer’ın giriş uçları olur.

A,B yetki uçları birleştirilir.Bu uçlar 8’den 1’e Multiplexer’ın b ve c

uçları olur. 4’ten 1’e Multiplexer’ların

enable uçları birleştirilirken biri değillenerek birleştirilir. Bu uçta 8’den

1’e Multiplexer’ın a ucu olur. 4’ten 1’e Multiplexerlar ‘ın çıkışları

OR kapısıyla birleştirilerek çıkışa verilir.

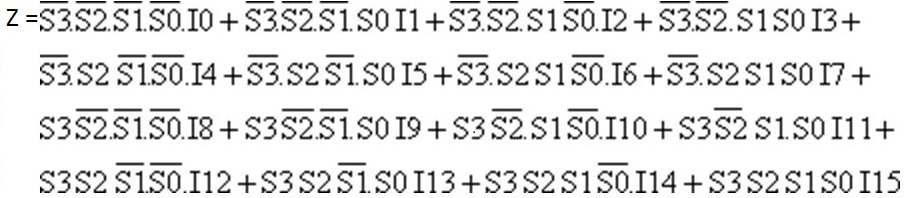

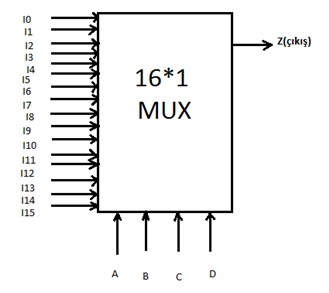

8.5.4 16’ dan 1’ e Multiplexer

16x1 MUX devresinde 16 giriş 1 çıkış ve 4 tane de kontrol girişi bulunur. Buna göre S3 = S2 = S1 = 0 ve S0 = 1 olduğu durumda çıkışa I1 girişi aktarılır. S2 = 1, ve S3 = S1 = S0 = 0 durumunda da çıkışa I4 girişi aktarılır.

Select bitlerinin tamamının 1 olduğu durumda çıkışta I15 girişi vardır. Buradan anlaşılacağı gibi Select bitlerinin aldığı çeşitli konumlara göre girişteki bilgilerden bir tanesi çıkışa aktarılır. Çıkış fonksiyonu (Z) Select bitlerinin aldığı konumlarla beraber girişlerinin çarpımlarına eşittir.

|

Tablo 8.29 16x1 MUX devresine uygun doğruluk tablosu |

Select Bits |

OUTPUT |

|||

S3 |

S2 |

S1 |

S0 |

Z |

0 |

0 |

0 |

0 |

I0 |

0 |

0 |

0 |

1 |

I1 |

0 |

0 |

1 |

0 |

I2 |

0 |

0 |

1 |

1 |

I3 |

0 |

1 |

0 |

0 |

I4 |

0 |

1 |

0 |

1 |

I5 |

0 |

1 |

1 |

0 |

I6 |

0 |

1 |

1 |

1 |

I7 |

1 |

0 |

0 |

0 |

I8 |

1 |

0 |

0 |

1 |

I9 |

1 |

0 |

1 |

0 |

I10 |

1 |

0 |

1 |

1 |

I11 |

1 |

1 |

0 |

0 |

I12 |

1 |

1 |

0 |

1 |

I13 |

1 |

1 |

1 |

0 |

I14 |

1 |

1 |

1 |

1 |

I15 |

|

|

Şekil 8.54 16*1 MUX devresinin lojik sembolü |

Örnek 8.20 16' dan 1' e multiplexer devresinin tasarlanması.

Örnek 8.21 2 adet 8x1 çoklayıcı ile 16x1 çoklayıcı devresi tasarlayınız.

8.5.5 Boolean Fonksiyonlarının ve Bileşik Devrelerinin Multiplexer ile Gerçekleştirilmesi

‘n’ değişkenli herhangi bir fonksiyonu, 2n-1 giriş / 1 çıkışlı çoklayıcı ile gerçekleştirmek

mümkündür. Boolean fonksiyonun çoklayıcı ile gerçekleştirilmesinde, n+1 değişkenli bir

fonksiyonun değişkenlerinden ‘n’ tanesi bir çoklayıcının seçme hatlarına bağlanırken, kalan

tek değişken çoklayıcı girişleri için kullanılır. Örneğin, ABC üç

değişkenli bir Boolean

fonksiyonunda A değişkeni, tek kalan değişken kabul edilip veri girişleri için kullanılırsa, çoklayıcı

girişleri A, A', 1, 0 değerlerinden birini alır. Bu dört değerin çoklayıcı girişlerine,

diğer değişkenlerin (B, C) seçici girişlere uygulanması ile, Boolean

fonksiyonun çoklayıcı ile gerçekleştirilmesi mümkün olur.

Verilen bir Boolean eşitliğini çoklayıcı yardımıyla

gerçekleştirmek için, çoklayıcı uygulama

tablolarının oluşturulması gerekir. Fonksiyonun uygulama tablolarının

oluşturulması ile, çoklayıcının girişlerine uygulanacak bilgiler bulunur.

|

|

Şekil 8.55 Boolean fonksiyonun çoklayıcı ile gerçekleştirilmesi |

Uygulama tablosu oluşturma işleminde takip edilecek sırayı, örnek bir uygulama ile birlikte

açıklayalım. Açıklama sırasında, üç değişkenli bir fonksiyonda en yüksek basamak

değerini

ifade eden A değişkeninin, giriş olarak kullanıldığını kabul edeceğiz.

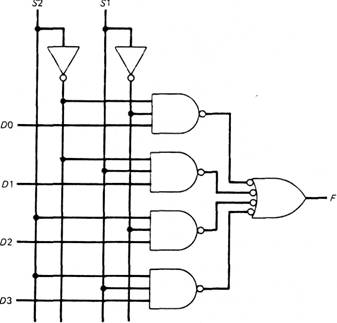

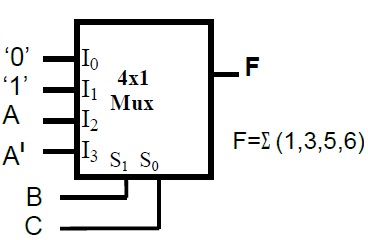

F(A,B,C)=S(1, 3, 5, 6) fonksiyonunun 4x1 çoklayıcı ile gerçekleştirilmesine yardım edecek

uygulama tablosunu çıkaralım:

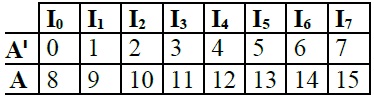

I) Boolean fonksiyonunun ifade ettiği değerler doğruluk tablosunda gösterilir.

Doğruluk tablosunda kombinasyonlar sıralanarak, çıkışta ‘1’ oluşması istenen

kombinasyonlar belirlenir (Tablo 8.17).

II)

Çoklayıcının girişlerinin isimleri yatay olarak yazılarak, altlarına iki sıra halinde

bütün mintermler sıralanır. Sıralamada, ilk satırda A=0 olan mintermler, ikinci satırda A=1 olan mintermler yer alır. İlk satır A', ikinci satır A olarak isimlendirilir

(Tablo 8.17.b).

III) Doğruluk tablosunda çıkışın ‘1’ olduğu minterm değerleri daire içine alınır

(Tablo

8.17.c).

IV) Her bir sütun ayrı ayrı incelenir. Bir sütundaki iki minterm daire içerisine

alınmışsa ilgili çoklayıcı girişine ‘1’, iki minterm

de daire içerisine alınmamışsa ilgili çoklayıcı girişinde ‘0’ bulunacağını

gösteren işaretleme yapılır.

V) Değişkenin kendisinin temsil edildiği alt minterm (örneğimizde A) daire içerisine

alınmışsa ilgili çoklayıcı girişine A, değişkenin değilinin (A') temsil edildiği minterm daire

içerisine alınmışsa ilgili çoklayıcı girişine A' uygulanacağını gösteren değerler verilir (Tablo

8.17.d). Böylece uygulama tablosu tamamlanır.

|

Tablo 8.30 Çoklayıcılarda doğruluk ve uygulama tablolarının oluşturulması |

| Multiplexer | A | B | C | F |

|

|

| 0 | 0 | 0 | 0 | 0 | ||

| 1 | 0 | 0 | 1 | 1 | ||

| 2 | 0 | 1 | 0 | 0 | ||

| 3 | 0 | 1 | 1 | 1 | ||

| 4 | 1 | 0 | 0 | 0 | ||

| 5 | 1 | 0 | 1 | 1 | ||

| 6 | 1 | 1 | 0 | 1 | ||

| 7 | 1 | 1 | 1 | 0 |

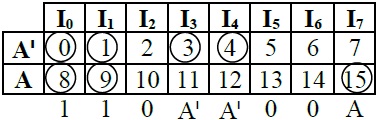

Elde edilen uygulama tablosunun 4x1 MUX devresine uygulanması ile,

Şekildeki

devre oluşur. Oluşan devrede, B ve C değişkenleri seçme girişlerine uygulanırken, çoklayıcı girişleri I0 = 0, I1 = 1, I2 = A, I3 = A' şeklinde değer alır.

Çoklayıcı girişlerine uygulanması gerekli değeri bulduğumuza göre seçme girişlerinin farklı durumlarında oluşacak çıkış değerlerini inceleyelim.

Seçici girişleri BC = 00 durumunda iken, I0 girişi seçilir ve I0 = 0 olduğundan F=0 olur.

Dolayısıyla iki kombinasyonda, yani m0 = A'B'C' ve m4 = AB'C' değerlerinde F = 0 olur. Çünkü,

BC = 00 iken, A değeri ne olursa olsun çıkış 0’dır.

BC = 01 iken I1 girişi seçilir ve I1 = 1 olduğundan F = 1 olur. Bunun anlamı, m1 = A'B'C ve

m5 = AB'C kombinasyonlarında F = 1 olmasıdır. Çünkü BC = 01 iken, A değeri ne olursa olsun çıkış 1’dir.

BC = 10 iken I2 girişi seçilir ve bu girişe A bağlı olduğu için m6 = ABC' kombinasyonunda

F = 1 olur. Ancak m2 = A'BC' kombinasyonu için A = 0 olacağından, F = 0 değerini alır.

Son olarak, BC = 11 olduğunda, I3 girişi seçilir ve bu girişe A' bağlı olduğu için m3 = A'BC

kombinasyonunda F = 1 olur. Ancak m7 = ABC kombinasyonu için F = 0

değerini alır. Bu bilgiler, Tablo 8.30’ deki doğruluk tablosunda özetlenen bilgilerin analitik açıklamasından

başka bir şey değildir.

Çoklayıcı girişlerindeki değişkenlerden en soldakini değil de başka bir

değişkeni çoklayıcı girişi olarak kullanmak istiyorsak, uygulama tablosunda gerekli değişikliği yapmak şartıyla istediğimiz değişkeni çoklayıcı girişi için seçebiliriz.

|

|

Şekil 8.56 F = S(1, 3, 5, 6) fonksiyonunun 4x1 MUX ile gerçekleştirilmesi |

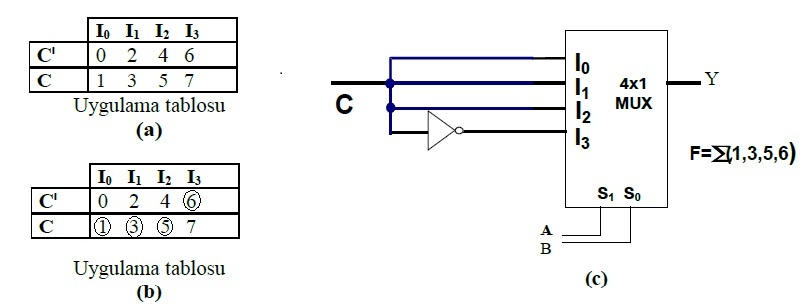

Örnek 8.22 F(ABC) = Σ(1, 3, 5, 6) fonksiyonunu 4x1 MUX ile gerçekleştireceğimizi ve S1ve S0 seçme girişleri için A ve B değişkenlerini, çoklayıcı girişleri için C değişkenini kullanacağımızı varsayalım. C değişkeni çift sayılarda tümlenip tek sayılarda tümlenemeyeceğinden, uygulama tablosundaki iki minterm satırının düzenlenmesi Şekildeki gibi oluşur.

|

|

Şekil 8.57 4x1 Çoklayıcı devre uygulaması |

F=Σ(1, 3, 5, 6) fonksiyonunu, oluşan tabloya yukarıdaki kuralları göz önüne alarak

uygularsak, Şekil 8.30.b’deki uygulama tablosu oluşur. Tablodan; I0 = C, I1 = C, I2 = C ve I3

= C’ bağlantılarının yapılması gerektiği bulunur. Uygulama tablosundan elde

edilen çıkış bağlantılarının yapılması ile Şekil 8.57.c’deki çoklayıcı devre bağlantısı ortaya çıkar.

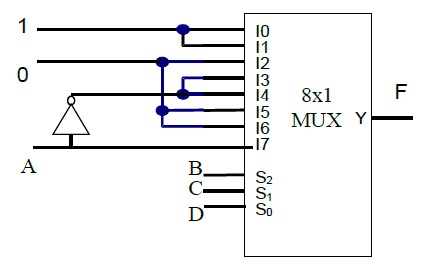

Örnek 8.23 F(A,B,C,D) = Σ(0, 1, 3, 4, 8, 9, 15) fonksiyonunu, 8x1 çoklayıcı ile tasarlanması.

Dört değişkenli bir fonksiyon olduğundan, üç seçme hattı ve sekiz girişli

bir çoklayıcıya ihtiyaç vardır. A değişkeni veri girişine, BCD değişkenleri

seçme girişlerine uygulanırsa, Şekil 8.58 ’deki uygulama tablosu oluşur.

|

|

Şekil 8.58 Uygulama tablosu |

|

|

Şekil 8.59 Uygulama tablosuna değerlerin yerleştirilmesi |

|

|

Şekil 8.60 Uygulama devresi |

Oluşan uygulama tablosunun ilk satırının A', ikinci satırının A olduğu göz önünde

bulundurulur ve fonksiyondaki minterm değerleri uygulama tablosuna taşınırsa,

Şekil 8.58 deki uygulama tablosu elde edilir.

Uygulama tablosundan elde edilen bilgilerin; 8x1 MUX’ a uyarlanması ile Şekil 8.60’deki

lojik devre oluşur.

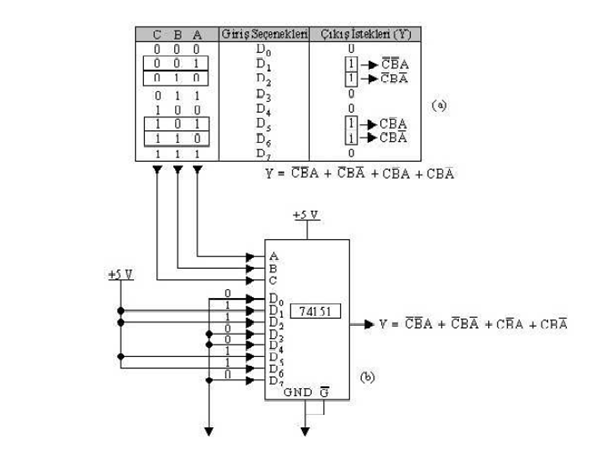

Giriş değişken sayısınca seçme girişi bulunan çoklayıcı kullanılması durumunda tablo

yapmaya gerek yoktur. Girişler doğrudan seçme girişlerine uygulanırken, çıkışın ‘1’ olmasının istendiği kombinasyonlar +Vcc’ ye, çıkışın ‘0’ olmasının istendiği kombinasyonlar

ise şaseye bağlanır (Şekil 8.59). Şekil 8.59.’deki tabloda çıkışın ‘1’ olmasının istendiği durumlar belirlenir. Girişler doğrudan

seçme girişlerine uygulanırken, çıkışın ‘1’ olmasının istendiği durumlar (D1, D2, D5, D6)

+Vcc’ ye, çıkışın ‘0’ olmasının istendiği durumlar ise (D0, D3, D4, D7) şaseye bağlanır.

|

|

Şekil 8.61 Lojik eşitliğin çoklayıcı ile gerçekleştirilmesi şekli |

8.5.6 Bileşik Devrelerin Çoklayıcı Kullanılarak Tasarlanması

Bileşik devreler doğrudan çoklayıcı kullanılarak tasarlanabilir. Tasarım sırasında genel olarak lojik devre tasarımında kullanılan işlem sırası takip edilir. Tasarım aşamalarını örnek uygulama ile inceleyelim.

Örnek 8.24 Aşağıda tasarım özellikleri verilen lojik devreyi 74151 çoklayıcı entegresi kullanarak gerçekleştirelim.

Tasarım özellikleri: Küçük bir şirketin 10 hissesi bulunmakta ve her hisse, hissedarlar toplantısında hisse sahibine bir oy hakkı vermektedir. 10 hissenin 4 hissedar arasındaki paylaşımı; Hissedar A = 1hisse , Hissedar B = 2 hisse, Hissedar C = 3 hisse, Hissedar D = 4 hisse şeklindedir. Hissedarların her birinin önünde, hisse sayısı oranı temsil eden ve evet için kapanan, hayır için açılan bir anahtar bulunmaktadır.

|

|

Şekil 8.62 8x1 mux ve 7447 kod çözücü ile çoklayıcı oluşturulması |

Yapılan oylamalarda, evet oyu veren toplam hisse sayısını gösteren bir devre tasarlanması istenmektedir. Bütün hissedarların karar için, evet oyu kullanması halinde ekranda ‘0’ görülmesi yeterlidir. Gerekli sayıyı göstermek için, 7 parçalı gösterge ve kod çözücü kullanılacaktır. Hissedarların anahtarlarından gelen verileri 7447 kod çözücü entegresinde kullanılacak şekilde BCD’ ye dönüştüren bileşik devreyi, dört adet 8 × 1 çoklayıcı entegresi (74151) kullanarak gerçekleştirelim.(Şekil

8.62)

1) Her bir hissedarın temsil ettiği oy oranı farklı olduğundan, hissedarların evet dedikleri zamandaki değerleri BCD’ ye çeviren doğruluk tablosu oluşturulur. Doğruluk tablosunda giriş değişkenleri olarak z, y, x, w harfleri, çıkış değişkenleri olarak FA, FB, FC, FD sembolleri kullanılacaktır.

2) Doğruluk tablosu çıkış sütunlarında oluşan bilgilerin her birisi

ayrı uygulama tablosuna taşınır.

3) Her biri 7447’ yi sürecek ikili bilgilerden birisini temsil eden çoklayıcı çıkışları elde edilir.

4) Uygulama tablosundaki verilen çoklayıcı bağlantısında kullanılması ile oluşturulan çoklayıcı çıkışları 7447 kod çevirici entegreyi sürmek için kullanılır (Tablo

8.31).

|

Tablo 8.31 8x1 mux ve 7447 kod çözücü doğruluk tablosu |

| Z | Y | X | W | FA | FB | FC | FD |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

|

|

Şekil 8.63 8x1 demux ve ve 74141 entegresi ile çoklayıcı oluşturulması |

Dört adet çoklayıcının çıkışlarından alınan bilgiler (FA, FB, FC, FD) 7447 entegresinin girişlerine verilirse, oylama sonucu elde edilen ve BCD koduna dönüştürülen sayı, yedi parçalı göstergede gözükür. Tüm hissedarların ‘Evet’ kullandığı durumda elde edilen onlu ‘10’ değerini göstermek için iki gösterge kullanılabilir.